一、What is makefile?

在 Linux(unix )环境下使用GNU 的make工具能够比较容易的构建一个属于你自己的工程,整个工程的编译只需要一个命令就可以完成编译、连接以至于最后的执行。不过这需要我们投入一些时间去完成一个或者多个称之为Makefile 文件的编写。

所要完成的Makefile 文件描述了整个工程的编译、连接等规则。其中包括:工程中的哪些源文件需要编译以及如何编译、需要创建那些库文件以及如何创建这些库文件、如何最后产生我们想要的可执行文件。

make是一个命令工具,它解释Makefile 中的指令(应该说是规则)。在Makefile文件中描述了整个工程所有文件的编译顺序、编译规则。Makefile 有自己的书写格式、关键字、函数。像C 语言有自己的格式、关键字和函数一样。而且在Makefile 中可以使用系统shell所提供的任何命令来完成想要的工作

二、makefile的规则

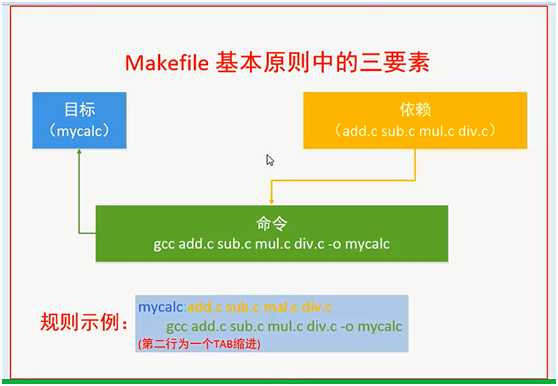

规则中的三要素:目标,依赖,命令

三、makefile子目标和终极目标的关系

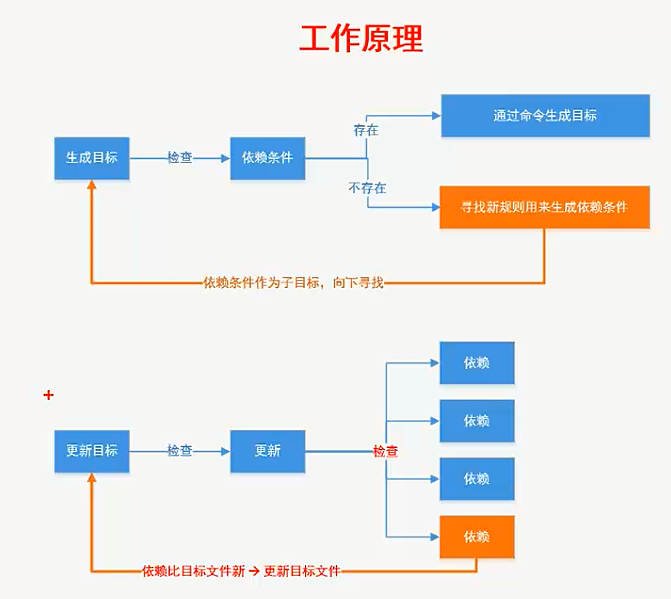

终极目标向下寻找依赖的子目标,子目标同理向下继续寻找所依赖的目标,直到最底层目标文件生成后,从下向上回归生成上层目标文件,最终生成终极目标文件.

四、makefile工作原理与更新目标的原则

makefile的工作原理是:makefile向下检索从而构建出一棵关系依赖树,从下向上执行命令,生成最终目标文件

makefile执行时,会检查依赖文件是否有更新改动,原则是按修改日期来检查,不断向下检查,如果检查到依赖文件有更新,就更新目标文件,最终更新最终目标文件

五、makefile常用的两个函数

1、查找指定目录下,指定类型的文件

wildcard 主要用于导入源代码文件

用法:src = $(wildcard ~/xxx/xxx/*.c)

2、匹配替换函数

patsubst 文件字符名的转换,主要用于从源代码文件名转换为目标文件名

用法:obj = $(patsubst %.c, %.o, $(src))

六、makefile的自动变量

常用自动变量

$<: 规则中的第一个依赖

$@: 规则中的目标

$^:规则中的所有依赖

注意:只能在规则中的命令中使用

DEMO:

src = $(wildcard *.cpp)

obj = $(patsubst %.cpp, %.o, $(src))

CPP = g++

CPPFLAGS = -Wall -g

Target = server

$(Target):$(obj)

$(CPP) $(obj) -o $@ $(CPPFLAGS)

%.o:%.cpp

$(CPP) $< -c $(CPPFLAGS)

.PHONY:clean all

clean:

rm $(Target) -f

Comments